- Modelsim altera full screen windows 10#

- Modelsim altera full screen verification#

- Modelsim altera full screen software#

VgaSim simulates a VGA screen connected to your VHDL design. All other school programs I use are working in linux, so I decided to make it work environment, while keeping windows only for gaming. Xilinx XSIM Browse The Most Popular 2 Matlab Vhdl Fpga Interpolation Overclock Open Source.

Modelsim altera full screen windows 10#

I have Windows 10 running on a separate SSD, but I feel kinda lazy to switch between OSs for just one program. I know I could run it on windows, quite easily, but I have separated my tasks, now finding myself using Linux for a greater part of my time. De cela naissent les « big data », ou « mégadonnées » comme souhaite les. Car les algorithmes modernes sont désormais capables de les faire « parler » pour extrapoler et en générer d’autres, plus complexes et plus complètes, par le jeu des corrélations. I have searched for guides, nothing seems to work, so I resort to you guys. Et il ne s’agit là que de celles liées au premier niveau d’analyse.

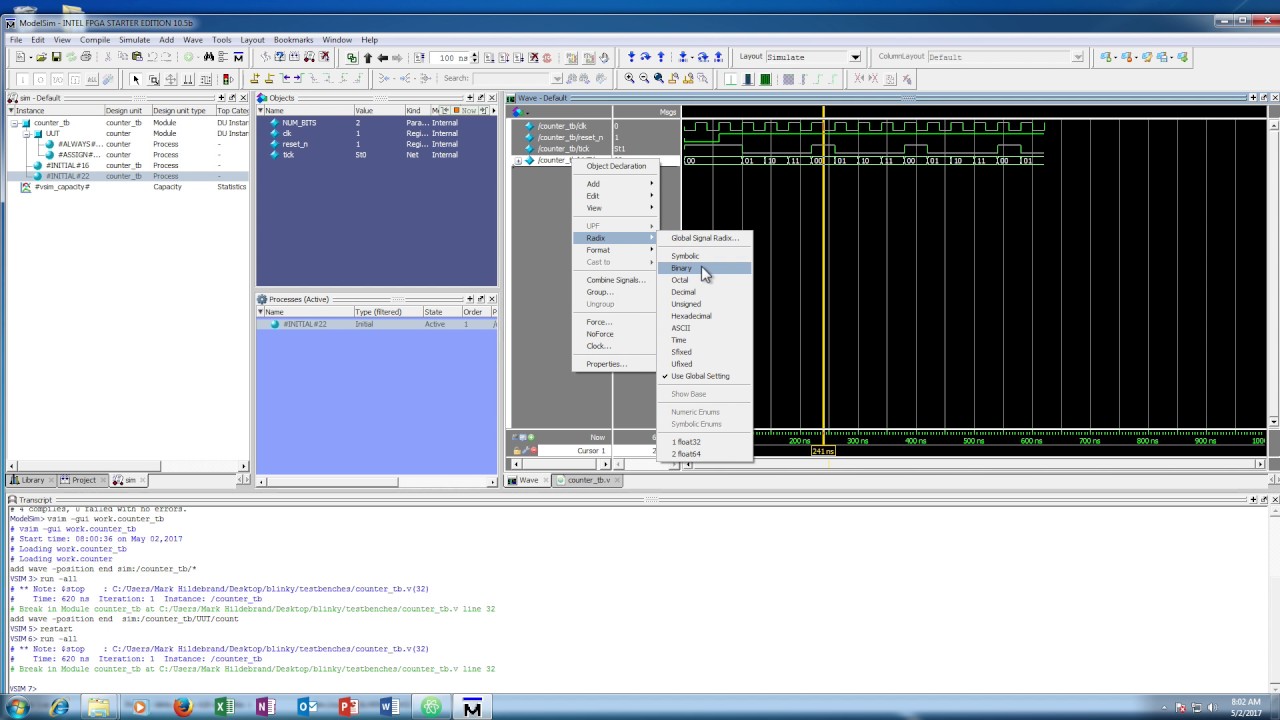

I have asked my teacher but apparently she is not that accustomed to working on Linux(although the computers we use at school do run Mint 17.3), nor did she point me to someone that does. I checked at school, with paths and whatnot, launchers.I created a launcher with vsim running in terminal, but all it does is briefly flashing a terminal window and then nothing. I've tried installing 32bit libraries as it is required to run ModelSim. One motivation for drawing your full adder schematic in Quartus II. Problem is, I can't get ModelSim to work separately, and for the love of God I cannot make it work. use a print screen (Snipping Tool in Win10). That works fine on linux, but because I have no board at home, it's quite useless for me. Additionally, the Slave ports have data width conversion capability to. Synthesis, STA and P&R by Quartus II (Altera).

Modelsim altera full screen verification#

RTL Design and Verification (Functional and Timing) using VerilogHDL on ModelSim. The number of filter taps is variable increasing toward thumb size decreasing to a minimum of 8 full screen size. We're also using Quartus II to program a Cyclone II C20F484C7(or sth like that) FPGA. The MPFE integrates easily into any Quartus II Qsys project. Full FPGA design flow: from Requirements Spec to FPGA programming.

Modelsim altera full screen software#

I am studying digital circuits atm at university and we are using this piece of software to simulate Verilog designs and see waveforms

0 kommentar(er)

0 kommentar(er)